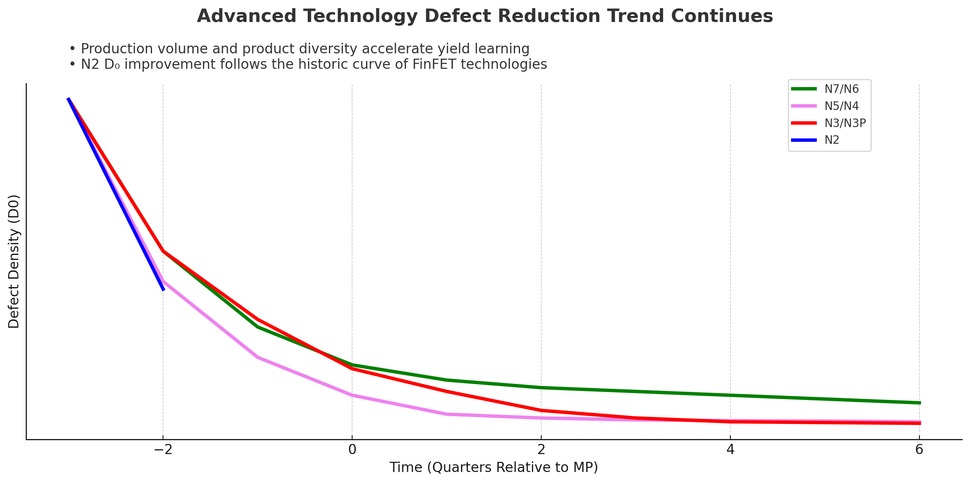

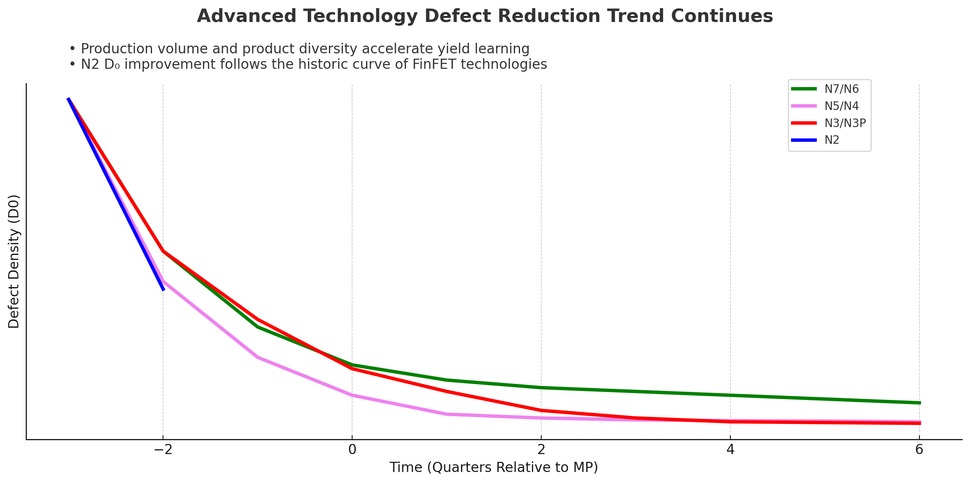

TSMC недавно объявил на североамериканском технологическом семинаре о плотности дефекта (D0) технологии процесса N2 (2NM) по сравнению с его предшественниками на том же этапе.Согласно компании, плотность дефектов процесса N2 ниже, чем у N3 (3NM), N5 (5NM) и N7 (7NM) узлов производства.Кроме того, слайд показывает, что процесс TSMC N2 все еще находится в двух четвертях от массового производства, что означает, что TSMC, как ожидается, начнет производить 2 -нм чипы к концу четвертого квартала 2025 года.

Хотя процесс TSMC N2 является первой технологией процесса компании, которая применила транзисторы для нанолиста полного кольца (GAA), плотность дефектов этого узла ниже, чем процесс предыдущего поколения на одной стадии, на два четверти впереди массового производства (MP).Процессы предыдущего поколения- N3/N3P, N5/N4 и N7/N6- все использовались транзисторы зрелого FIN-эффекта (FINFETS).Следовательно, хотя N2 является первым узлом TSMC для принятия транзисторов GAA нанолиста, его снижение плотности дефектов больше, чем процесс предыдущего поколения, прежде чем вступить в веху массового производства (HVM).

Эта диаграмма изображает изменение плотности дефектов с течением времени, охватывающего от трех четвертей до массового производства до шести кварталов после массового производства.Среди всех отображаемых узлов - N7/N6 (зеленый), N5/N4 (фиолетовый), N3/N3P (красный) и N2 (синий) - плотность дефекта значительно уменьшается с увеличением урожайности, но скорость уменьшения варьируется в зависимости от сложности узлов.Стоит отметить, что N5/N4 является наиболее активным в снижении ранних дефектов, в то время как улучшение урожайности N7/N6 является относительно нежным.Начальный уровень дефекта кривой N2 выше, чем у N5/N4, но затем резко уменьшается, что очень близко к траектории уменьшения дефекта N3/N3P.

Слайд подчеркивает, что урожайность и разнообразие продуктов остаются ключевыми движущими факторами для ускоряющегося улучшения плотности дефекта.Более высокие производственные и диверсифицированные продукты с использованием того же процесса могут идентифицировать и исправлять плотность дефектов и быстрее доставлять проблемы, что позволяет TSMC оптимизировать циклы обучения дефектов.TSMC заявил, что его технология производства N2 получила больше новых чипов, чем ее технология предшественника (поскольку TSMC теперь производит чипы N2 для клиентов для смартфонов и высокопроизводительных вычислений (HPC) в риске), а кривая снижения плотности дефекта в основном подтверждает это.

Учитывая факторы риска, вызванные введением новой транзисторной архитектуры, особенно важно, чтобы скорость снижения дефекта N2 оставалась в соответствии с предыдущими узлами на основе FINFET.Это указывает на то, что TSMC успешно передала свой опыт обучения процесса и управления дефектами в новую эру Гаафета, не столкнувшись с значительными неудачами.

RFQs/ORDER (0)

RFQs/ORDER (0)

RFQs/ORDER (0)

RFQs/ORDER (0)